LimeSDR-USB主板功能

LimeSDR-USB开发板提供了一个高效的射频硬件平台,使用Altera Cyclone IV FPGA和LMS7002M收发器开发和原型化高性能和逻辑密集型数字设计和RF设计。

LimeSDR-USB板功能

USB接口:赛普拉斯FX3超高速USB第3代控制器

FPGA功能:Cyclone IV EP4CE40F23C8N器件采用484引脚FPGA;39’600逻辑元素;1134 Kbits嵌入式内存;116个嵌入式18×18乘法器;4个PLL

FPGA配置:JTAG模式配置;主动串行模式配置;使用FX3(USB)更新FPGA器件的可能性

记忆设备:2 x 1Gbit(64M x 16)DDR2 SDRAM;FX3固件的4Mbit闪存;用于FPGA器件的16Mbit闪存;2 x 128K(16K x 8)EEPROM,用于LMS MCU固件,LMS MCU数据;用于FX3数据的1 x 64K(8K x 8)EEPROM

连接:microUSB3.0(B型)连接器或USB3.0(A型)插头;同轴RF(U.FL)连接器;FPGA GPIO接头(0.05“间距);FPGA和FX3 JTAG连接器(0.05“间距);6-12V DC电源插孔和pinheader;风扇连接器(3.3V)

时钟系统:30.72MHz VCTCXO(精度:初始±1 ppm,稳定±4 ppm);可以通过板载DAC将VCTCXO锁定到外部时钟或调谐VCTCXO;用于FPGA参考时钟输入或LMS PLL的可编程时钟发生器

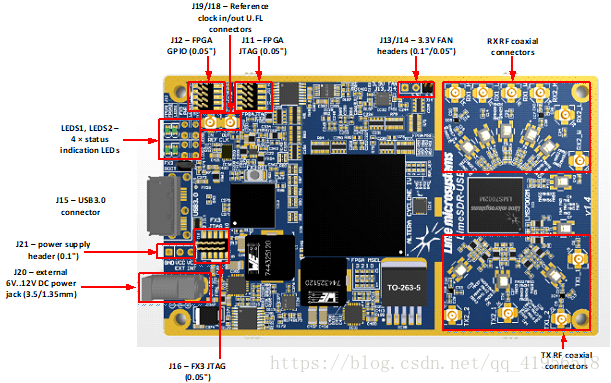

LimeSDR-USB硬件概述

LimeSDR-usb有三种连接器类型:

数据和调试(USB3.0,FPGA GPIO和JTAG)

电源(DC插孔和外部电源pinheader)

高频(RF)和参考时钟)

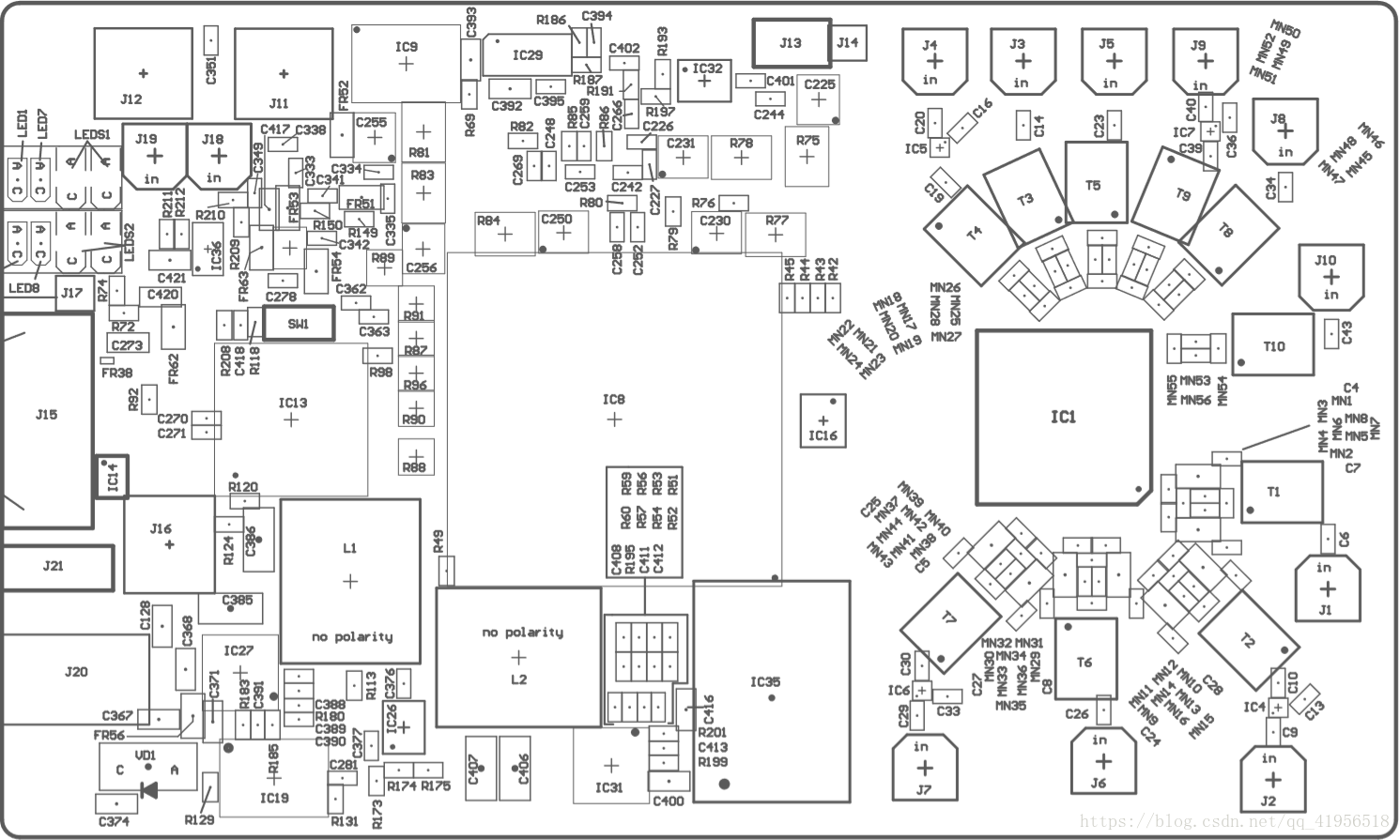

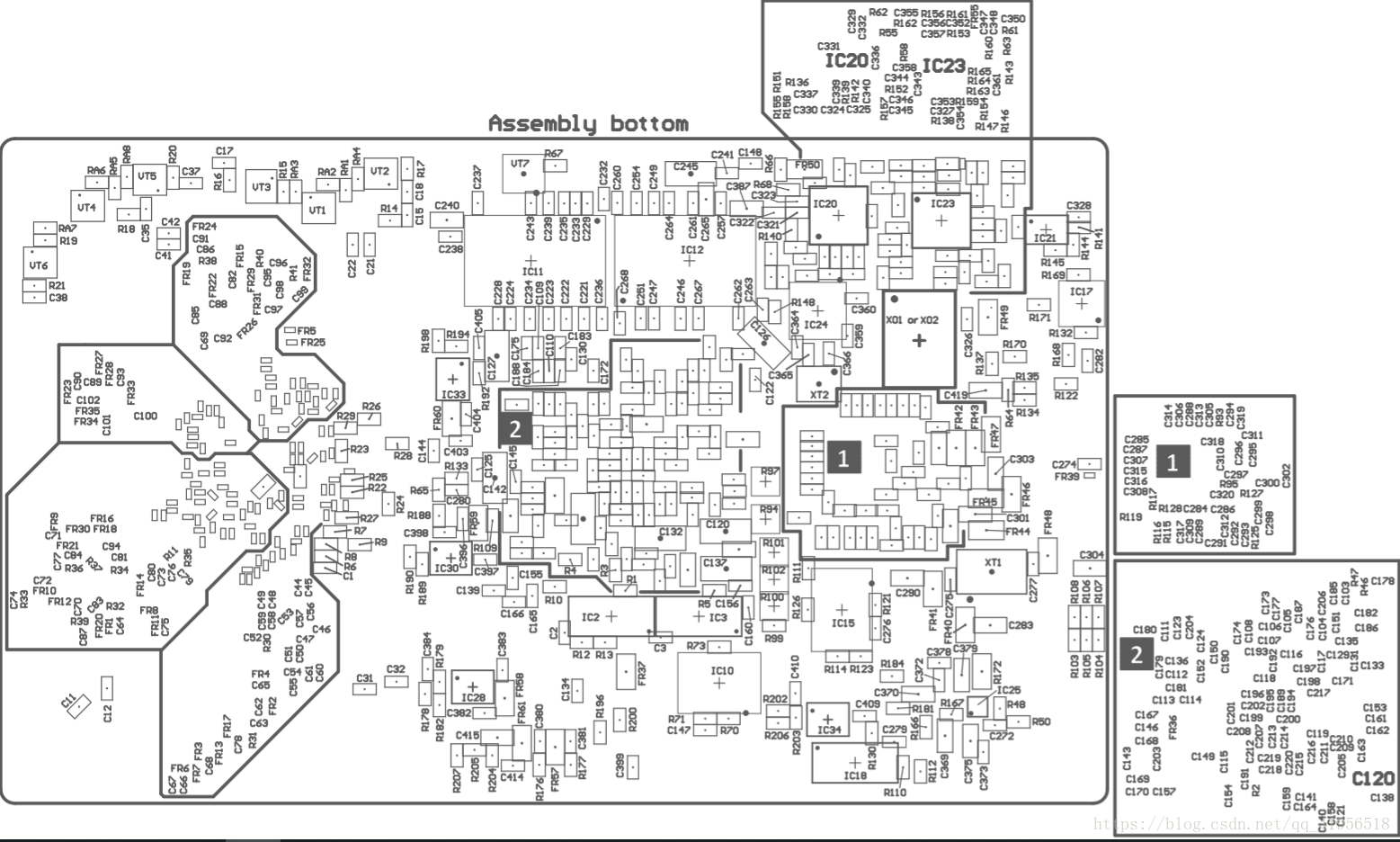

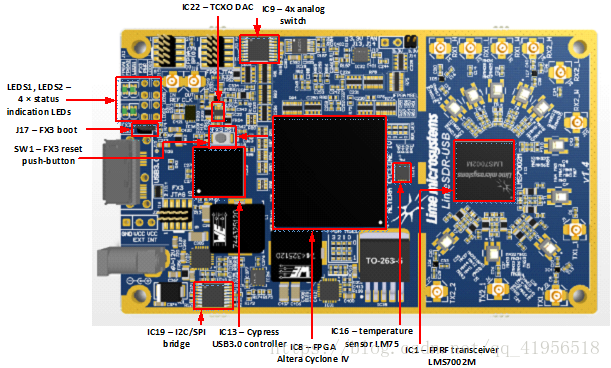

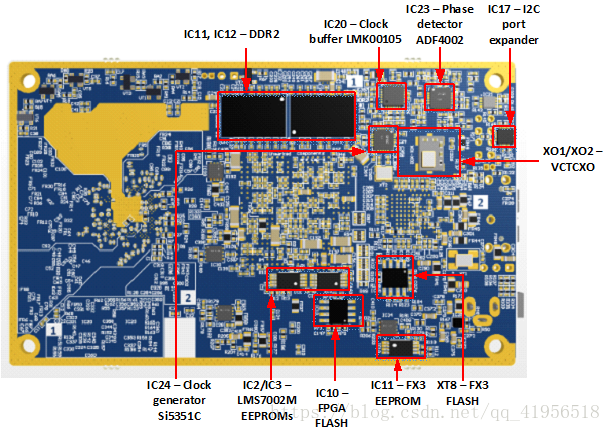

下面分别是LimeSDR-USB的PCB与实物参考图

核心部分

1. IC1 – FPRF 现场可编程RF收发器,LMS7002M

2. IC8 – FPGA Altera Cyclone IV,EP4CE40F23C8N 484-BGA

3. IC13 – USB 3.0微控制器,赛普拉斯FX3超高速USB第3代控制器,CYUSB3014

一般部件

4. IC9 – 四路SPDT开关,TS3A5018PW

5. IC6 – 温度传感器,LM75

6. IC19 – SPI至I²C,SC18IS602BIPW(未安装)

7. IC17 – I²C端口扩展器,带有4个推挽输出和4个输入,MAX7322ATE +

配置部件

IC9 – 四路SPDT开关,TS3A5018PW

R51,R52,R53,R54,R56,R57,R59,R60 – 0欧姆电阻器 FPGA(IC31)MSEL [3:0]。默认模式:Active Serial Standard配置

R115,R116,R117 – 10 kOhm电阻 – USB3.0微控制器(IC13)启动配置(PMODE0 [2:0])电阻。默认模式:SPI启动,开启失败 – USB启动

R125,R127,R128 10 kOhm电阻 – USB3.0微控制器(IC13)晶振/时钟频率选择(FSLC [2:0])电阻。默认模式:19.2MHz晶振

J16 – JTAG链引脚头 USB3.0(IC6)微控制器的调试引脚头,0.05“间距

J17,R122 针接头 – USB3.0微控制器启动源(闪存或USB),0.05“跳线跳线或0402 0R电阻。在正常操作中,必须放置跳线或电阻器。

SW1 – 按钮式 USB3.0微控制器复位按钮

J11 – JTAG链引脚头 用于Altera USB-Blaster下载电缆的FPGA编程引脚接头,间距为0.05“

LEDS1 – 红绿状态LED 用户定义的FPGA指示LED1(如果是SMD,则在板边缘附近;如果是通孔则在底部),用户定义的FPGA指示LED2(如果是SMD则更远的板边缘;如果是通孔,则在顶部)

LEDS2 – 红绿状态LED FX3(USB)状态指示LED(如果是SMD,则位于板边缘附近;如果是通孔,则位于底部),板电源指示LED(如果是SMD,则为更远的板边;如果是通孔则位于顶部)

其他输出端口

J12 – 8个FPGA GPIO,0.05“间距

J13,J14 – 3.3V风扇连接引脚头,分别为0.1“和0.05”间距

储存设备

IC11,IC12 – DDR2内存 1Gbit(64M x 16)DDR2 SDRAM,带有16位数据总线

IC2,IC3 – 128K(16K x 8)带电可擦可编程只读存储器,LMS7002 MCU固件,LMS7002M数据

IC18 – 64K(8K x 8)带电可擦可编程只读存储器,连接到主I2C总线

IC10 – 闪存 用于FPGA配置的16Mbit Flash

IC15 – 闪存 适用于FX3固件的4Mbit Flash

通信端口

J15 – USB3.0连接器 microUSB3.0(B型)连接器或USB3.0(A型)插头

时钟电路

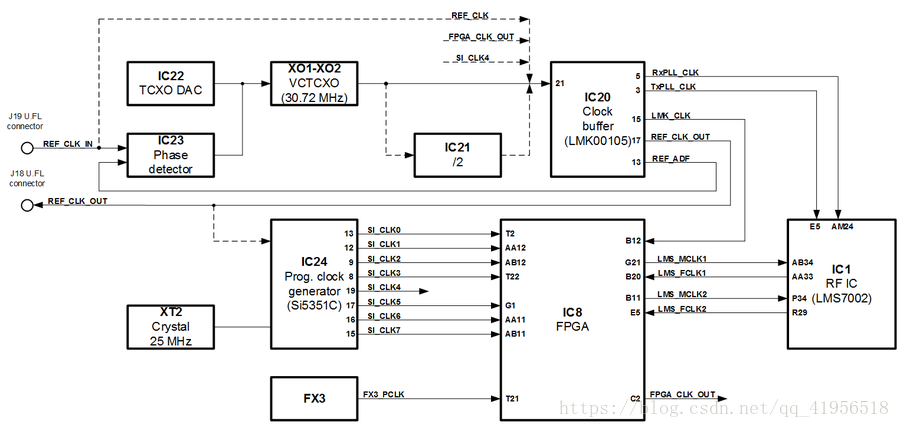

XO1,XO2 – VCTCXO 30.72MHz压控晶体振荡器

IC24 – 可编程时钟发生器,用于FPGA参考时钟输入和RF板

IC23 – ADF4002鉴相器

IC22 – 用于TCXO(XT4)频率调谐的DAC

J19 – U.FL连接器 参考时钟输入

J18 – U.FL连接器 参考时钟输出

电源

J20 – 外部6-12V直流电源

J21 – 外部6-12V直流电源和主内部电源轨

LimeSDR-USB硬件架构

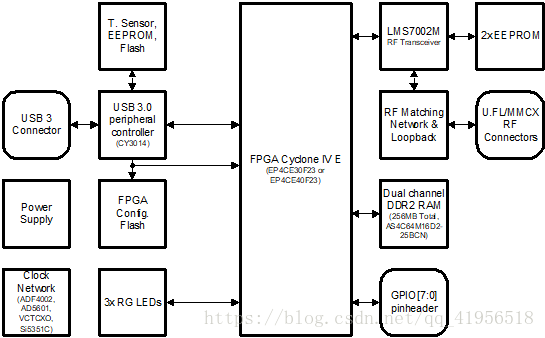

LimeSDR-USB板的核心是Altera Cyclone IV FPGA。其主要功能是通过USB3.0连接器在PC之间传输数字数据。

基于LMS7002M的连接

数字接口信号:LMS7002使用数据总线LMS_DIQ1_D [11:0]和LMS_DIQ2_D [11:0],和LMS_ENABLE_IQSEL1 LMS_ENABLE_IQSEL2,LMS_FCLK1和LMS_FCLK2,LMS_MCLK1和LMS_MCLK2信号将数据从FPGA传送到/。索引1和2表示收发器数字数据PORT-1或PORT-2。这些端口中的任何一个都可用于传输或接收数据。默认情况下,PORT-1被选为发送端口,PORT-2被选为接收端口。FCLK#是输入时钟,MCLK#是LMS7002M收发器的输出时钟。TXNRX信号设置端口方向。有关LMS7002M接口时序的详细信息,请参阅LMS7002M收发器数据表。

LMS控制信号:这些信号用于可选功能:

LMS_RXEN,LMS_TXEN – 接收器和发送器启用/禁用连接到FPGA Bank8(VDIO_LMS_FPGA;2.5V)的信号。

LMS_RESET – LMS7002M复位连接到FPGA Bank 7(VDIO_LMS_FPGA; 2.5V)。

SPI接口:LMS7002M收发器通过4线SPI接口配置; FPGA_SPI0_SCLK,FPGA_SPI0_MOSI,FPGA_SPI0_MISO,FPGA_SPI0_LMS_SS。SPI接口由FPGA Bank 8(VDIO_LMS_FPGA; 2.5V)控制。

主I2C接口:用于控制LimeSDR-USB板上的外部时钟合成器,端口扩展器,温度传感器,EEPROM,I2C-SPI桥接器。信号FX3_I2C_SCL,FX3_I2C_SDA连接到FX3。这些I2C线路也通过0R电阻连接到FPGA Bank 8(VCC3P3; 3.3V)线FPGA_I2C_SCL,FPGA_I2C_SDA。

LMS I2C接口:可用于LMS EEPROM内容修改或用于调试目的。信号LMS_I2C_SCL,LMS_I2C_DATA连接到FPGA Bank 8(VDIO_LMS_FPGA; 2.5V)。

时钟电路

LimeSDR-USB板具有板载30.72 MHz VCTCXO(精度:±1 ppm初始值,±4 ppm稳定值),是LMS_PLL的参考时钟。VCTCXO可通过板载相位检测器(IC23,ADF4002)或DAC(IC22)进行调谐。板载频率合成器用于将板载VCTCXO与外部设备(通过J19 U.FL连接器)同步,以校准频率误差。同时只有ADF或DAC可以控制VCTCXO。ADF和DAC之间的选择自动完成。当电路板上电时,默认情况下VCTCXO由DAC控制。可编程时钟发生器(Si5351C)可以产生任何参考时钟频率,从8 kHz – 160 MHz开始,用于FPGA和LMS PLL。

———————

作者:NVASPC

来源:CSDN

原文:https://blog.csdn.net/qq_41956518/article/details/81953610

版权声明:本文为博主原创文章,转载请附上博文链接!

0 条评论